¥0.69

价格更新:2025-03-07博斯克质量保证

Overview

These parallel-in or serial-in, serial-out registers feature gated clock (CLK, CLK INH) inputs and an overriding clear (CLR)\ input. The parallel-in or serial-in modes are established by the shift/load (SH/LD)\ input. When high, SH/LD\ enables the serial (SER) data input and couples the eight flip-flops for serial shifting with each clock (CLK) pulse. When low, the parallel (broadside) data inputs are enabled, and synchronous loading occurs on the next clock pulse. During parallel loading, serial data flow is inhibited. Clocking is accomplished on the low-to-high-level edge of CLK through a 2-input positive-NOR gate permitting one input to be used as a clock-enable or clock-inhibit function. Holding either CLK or CLK INH high inhibits clocking; holding either low enables the other clock input. This allows the system clock to be free running, and the register can be stopped on command with the other clock input. CLK INH should be changed to the high level only when CLK is high. CLR\ overrides all other inputs, including CLK, and resets all flip-flops to zero.

These parallel-in or serial-in, serial-out registers feature gated clock (CLK, CLK INH) inputs and an overriding clear (CLR)\ input. The parallel-in or serial-in modes are established by the shift/load (SH/LD)\ input. When high, SH/LD\ enables the serial (SER) data input and couples the eight flip-flops for serial shifting with each clock (CLK) pulse. When low, the parallel (broadside) data inputs are enabled, and synchronous loading occurs on the next clock pulse. During parallel loading, serial data flow is inhibited. Clocking is accomplished on the low-to-high-level edge of CLK through a 2-input positive-NOR gate permitting one input to be used as a clock-enable or clock-inhibit function. Holding either CLK or CLK INH high inhibits clocking; holding either low enables the other clock input. This allows the system clock to be free running, and the register can be stopped on command with the other clock input. CLK INH should be changed to the high level only when CLK is high. CLR\ overrides all other inputs, including CLK, and resets all flip-flops to zero.

Features

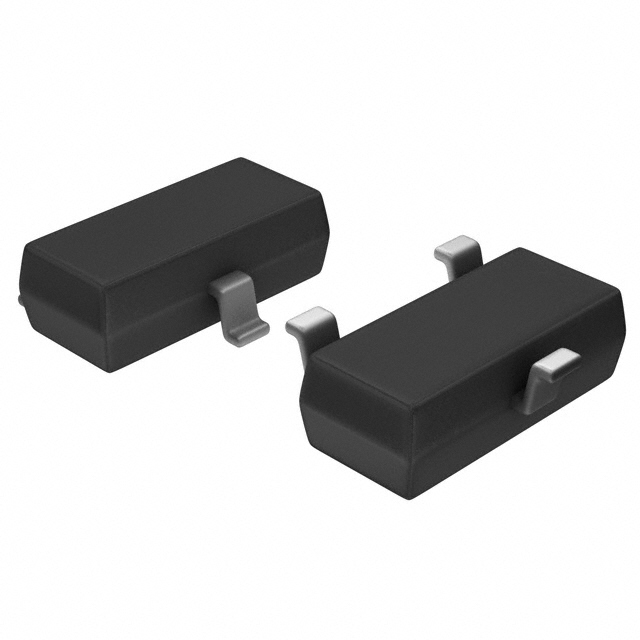

74HC SeriesWith 16 pins

Mounted in Surface Mount type.

Based on 74HC166 family

Operate supply voltage at 5V

It supplies 2/6V power

With 3 output lines

Quiescent Current at 8μA

Packing Method : TR

Surface Mount Mounting Type

Applications

There are a lot of Texas Instruments

SN74HC166DR Shift Registers applications.

- Pseudo Random Pattern Generator

- Pulse Extenders

- Pattern Recognizers

- Interconnectors

- Counter

- Data manipulation

- Delay Line

- Generate time delay toward digital circuits

- Parallel data

- Parallel to serial converter

- 起步价为$40,南非、巴西、印度、巴基斯坦、以色列等国家的价格会有所变动,详情请咨询相关客服人员。

- 包裹重量≤0.5kg的基本运费根据时区和国家而定。

- 我们的产品目前使用DHL,顺丰和UPS运输。如果数量少,则选择联邦快递。

- 一旦发货,预期交货时间跟选择的运输方式有所变动。

准备产品

真空包装

防静电袋

单独包装

包装盒

条形码运输标签

Texas Instruments

Texas Instruments(TI)是一家全球领先的半导体公司,专注于模拟和嵌入式处理器的设计和制造。公司成立于1930年,总部位于美国德克萨斯州达拉斯。TI的产品广泛应用于工业、汽车、个人电子、通信设备和企业系统等领域,致力于通过半导体技术推动电子设备的创新和普及。

热门零件号

实时新闻

博斯克数字

收入: 85M

2022年的收入为8500万美元,与2021年增长63%。

国家: 105

博斯克服务全球105个国家的客户。

配件发货: 25M+

我们在过去的五年中发货了2.5亿个配件,比前五年增长148%。

制造商: 950

2022年,博斯克从近950个制造商售卖了配件。

热门产品

ACS758LCB-100B-PFF-T

Allegro MicroSystems

SENSOR CURRENT HALL 100A 5-CB

A1326LLHLT-T

Allegro MicroSystems

SENSOR HALL EFFECT ANALOG SOT23W

A4982SLPTR-T

Allegro MicroSystems

IC MTR DRV BIPOLR 3-5.5V 24TSSOP

A3938SLDTR-T

Allegro MicroSystems

IC MOTOR DRIVER 18V-50V 38TSSOP

A4989SLDTR-T

Allegro MicroSystems

IC MTR DRV BIPOLR 3-5.5V 38TSSOP

ACS758LCB-100U-PFF-T

Allegro MicroSystems

SENSOR CURRENT HALL 100A 5-CB

A3988SEVTR-T

Allegro MicroSystems

IC MTR DRVR BIPOLAR 3-5.5V 36QFN

ACS712ELCTR-05B-T

Allegro MicroSystems

SENSOR CURRENT HALL 5A AC/DC

A3906SESTR-T

Allegro MicroSystems

IC MTR DRVR BIPOLAR 2.5-9V 20QFN

ACS713ELCTR-30A-T

Allegro MicroSystems

SENSOR CURRENT HALL 30A DC