¥480.00

价格更新:一个月前博斯克质量保证

Overview

— PowerPC architecture-compliant memory management unit (MMU) — Common on-chip processor (COP) test interface — High-performance (6.6–7.65 SPEC95 benchmark at 300 MHz; 1.68 MIPs/MHz without inlining and 1.90 Dhrystones MIPS/MHz with — Supports bus snooping for data cache coherency — Floating-point unit (FPU) • Separate power supply for internal logic and for I/O • Separate PLLs for G2 core and for the CPM — G2 core and CPM can run at different frequencies for power/performance optimization — Internal core/bus clock multiplier that provides 1.5:1, 2:1, 2.5:1, 3:1, 3.5:1, 4:1, 5:1, 6:1 ratios — Internal CPM/bus clock multiplier that provides 2:1, 2.5:1, 3:1, 3.5:1, 4:1, 5:1, 6:1 ratios • 64-bit data and 32-bit address 60x bus — Bus supports multiple master designs — Supports single- and four-beat burst transfers — 64-, 32-, 16-, and 8-bit port sizes controlled by on-chip memory controller — Supports data parity or ECC and address parity • 32-bit data and 18-bit address local bus — Single-master bus, supports external slaves — Eight-beat burst transfers — 32-, 16-, and 8-bit port sizes controlled by on-chip memory controller • 60x-to-PCI bridge (MPC8265 and MPC8266 only) — Programmable host bridge and agent — 32-bit data bus, 66 MHz, 3.3 V — Synchronous and asynchronous 60x and PCI clock modes — All internal address space available to external PCI host — DMA for memory block transfers — PCI-to-60x address remapping • System interface unit (SIU) — Clock synthesizer — Reset controller — Real-time clock (RTC) register — Periodic interrupt timer — Hardware bus monitor and software watchdog timer — IEEE Std. 1149.1™ standard JTAG test access port • Twelve-bank memory controller — Glueless interface to SRAM, page mode SDRAM, DRAM, EPROM, Flash and other userdefinable peripherals — Byte write enables and selectable parity generation — PowerPC architecture-compliant memory management unit (MMU) — Common on-chip processor (COP) test interface — High-performance (6.6–7.65 SPEC95 benchmark at 300 MHz; 1.68 MIPs/MHz without inlining and 1.90 Dhrystones MIPS/MHz with — Supports bus snooping for data cache coherency — Floating-point unit (FPU) • Separate power supply for internal logic and for I/O • Separate PLLs for G2 core and for the CPM — G2 core and CPM can run at different frequencies for power/performance optimization — Internal core/bus clock multiplier that provides 1.5:1, 2:1, 2.5:1, 3:1, 3.5:1, 4:1, 5:1, 6:1 ratios — Internal CPM/bus clock multiplier that provides 2:1, 2.5:1, 3:1, 3.5:1, 4:1, 5:1, 6:1 ratios • 64-bit data and 32-bit address 60x bus — Bus supports multiple master designs — Supports single- and four-beat burst transfers — 64-, 32-, 16-, and 8-bit port sizes controlled by on-chip memory controller — Supports data parity or ECC and address parity • 32-bit data and 18-bit address local bus — Single-master bus, supports external slaves — Eight-beat burst transfers — 32-, 16-, and 8-bit port sizes controlled by on-chip memory controller • 60x-to-PCI bridge (MPC8265 and MPC8266 only) — Programmable host bridge and agent — 32-bit data bus, 66 MHz, 3.3 V — Synchronous and asynchronous 60x and PCI clock modes — All internal address space available to external PCI host — DMA for memory block transfers — PCI-to-60x address remapping • System interface unit (SIU) — Clock synthesizer — Reset controller — Real-time clock (RTC) register — Periodic interrupt timer — Hardware bus monitor and software watchdog timer — IEEE Std. 1149.1™ standard JTAG test access port • Twelve-bank memory controller — Glueless interface to SRAM, page mode SDRAM, DRAM, EPROM, Flash and other userdefinable peripherals — Byte write enables and selectable parity generation – Transparent – UART (low-speed operation) — One serial peripheral interface identical to the MPC860 SPI — One inter-integrated circuit (I2 C) controller (identical to the MPC860 I2 C controller) – Microwire compatible – Multiple-master, single-master, and slave modes — Up to eight TDM interfaces (four on the MPC8255) – Supports two groups of four TDM channels for a total of eight TDMs – 2,048 bytes of SI RAM – Bit or byte resolution – Independent transmit and receive routing, frame synchronization – Supports T1, CEPT, T1/E1, T3/E3, pulse code modulation highway, ISDN basic rate, ISDN primary rate, Freescale interchip digital link (IDL), general circuit interface (GCI), and user-defined TDM serial interfaces — Eight independent baud rate generators and 20 input clock pins for supplying clocks to FCCs, SCCs, SMCs, and serial channels — Four independent 16-bit timers that can be interconnected as two 32-bit timers Additional features of the MPC826xA family are as follows: • CPM — 32-Kbyte dual-port RAM — Additional MCC host commands — Eight transfer transmission convergence (TC) layers between the TDMs and FCC2 to support inverse multiplexing for ATM capabilities (IMA) (MPC8264 and MPC8266 only) • CPM multiplexing — FCC2 can also be connected to the TC layer. • TC layer (MPC8264 and MPC8266 only) — Each of the 8 TDM channels is routed in hardware to a TC layer block – Protocol-specific overhead bits may be discarded or routed to other controllers by the SI – Performing ATM TC layer functions (according to ITU-T I.432) – Transmit (Tx) updates - Cell HEC generation - Payload scrambling using self synchronizing scrambler (programmable by the user) - Coset generation (programmable by the user) - Cell rate by inserting idle/unassigned cells – Receive (Rx) updates - Cell delineation using bit by bit HEC checking and programmable ALPHA and DELTA parameters for the delineation state machine - Payload descrambling using self synchronizing scrambler (programmable by the user)

• Communications processor module (CPM)

Features

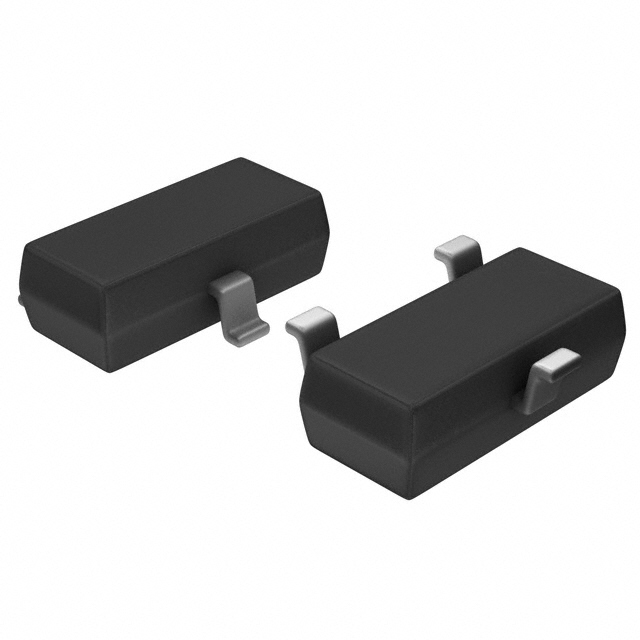

PowerPC G2 Core

32-Bit Structure

Bulk Package

Applications

There are a lot of NXP USA Inc.

XPC8260VVHFBC Microprocessor applications.

- Toys

- Robots

- Radio

- Television

- Heater/Fan

- Calculator

- Kindle

- Christmas lights

- 3D printers

- Washing machine

- 起步价为$40,南非、巴西、印度、巴基斯坦、以色列等国家的价格会有所变动,详情请咨询相关客服人员。

- 包裹重量≤0.5kg的基本运费根据时区和国家而定。

- 我们的产品目前使用DHL,顺丰和UPS运输。如果数量少,则选择联邦快递。

- 一旦发货,预期交货时间跟选择的运输方式有所变动。

准备产品

真空包装

防静电袋

单独包装

包装盒

条形码运输标签

NXP USA Inc.

NXP USA Inc.是NXP Semiconductors在美国的子公司,负责设计、研发、制造和销售半导体产品。公司在德克萨斯州奥斯汀和亚利桑那州钱德勒设有晶圆制造设施,专注于为汽车、工业和通信市场提供高性能解决方案。

热门零件号

实时新闻

博斯克数字

收入: 85M

2022年的收入为8500万美元,与2021年增长63%。

国家: 105

博斯克服务全球105个国家的客户。

配件发货: 25M+

我们在过去的五年中发货了2.5亿个配件,比前五年增长148%。

制造商: 950

2022年,博斯克从近950个制造商售卖了配件。

热门产品

FS32K144UAT0VLLT

NXP USA Inc.

IC MCU 32BIT 512KB FLASH 100LQFP

MKL03Z32VFK4R

NXP USA Inc.

IC MCU 32BIT 32KB FLASH 24QFN

MK22FN512VDC12

NXP USA Inc.

IC MCU 32BIT 512KB FLSH 121XFBGA

MK20DX256VMC10

NXP USA Inc.

IC MCU 32B 256KB FLASH 121MAPBGA

MC9S08PA8AVTJ

NXP USA Inc.

IC MCU 8BIT 8KB FLASH 20TSSOP

MIMXRT1064DVL6B

NXP USA Inc.

IC MCU 32BIT 4MB FLASH 196MAPBGA

MK64FX512VLL12

NXP USA Inc.

IC MCU 32BIT 512KB FLASH 100LQFP

MKL17Z256VFT4R

NXP USA Inc.

IC MCU 32BIT 256KB FLASH 48QFN

MC9S12XEP100MAG

NXP USA Inc.

IC MCU 16BIT 1MB FLASH 144LQFP

LPC54616J512ET100E

NXP USA Inc.

IC MCU 32BIT 512KB FLSH 100TFBGA