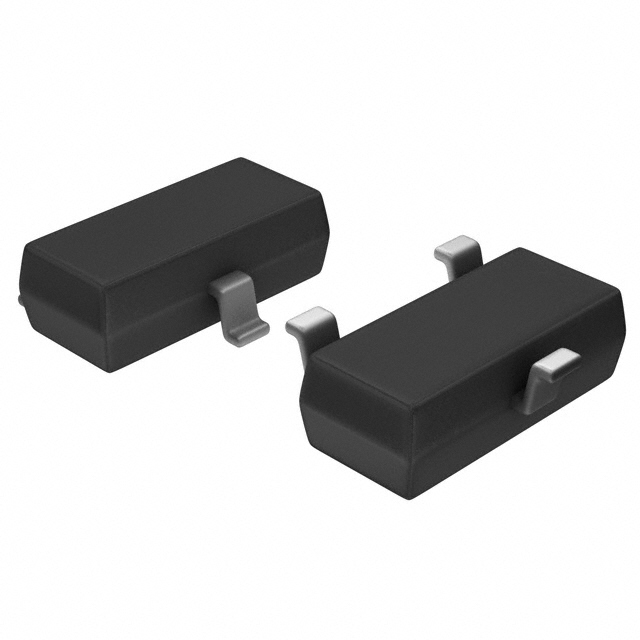

NXP PCA9617ATPZ

缓冲器,转接驱动器2 线式总线2 线式总线1MHz1

比较

¥18.00

价格更新:一个月前博斯克质量保证

Overview

The is a CMOS integrated circuit that provides level shifting between low voltage 5.5 V) and higher voltage 5.5 V) Fast-mode Plus (Fm+) I2C-bus or SMBus applications. While retaining all the operating modes and features of the I2C-bus system during the level shifts, it also permits extension of the I2C-bus by providing bidirectional buffering for both the data (SDA) and the clock (SCL) lines, thus enabling two buses at 1 MHz pF at lower speeds. Using the PCA9617ATPZ enables the system designer to isolate two halves of a bus for both voltage and capacitance. The SDA and SCL pins are overvoltage tolerant and are high-impedance when the PCA9617ATPZ is unpowered. The 5.5 V bus port B drivers have the static level offset, while the adjustable voltage bus port A drivers eliminate the static offset voltage. This results in a LOW on the port B translating into a nearly 0 V LOW on the port A which accommodates the smaller voltage swings of lower voltage logic. The static offset design of the port B PCA9617ATPZ I/O drivers prevents them from being connected to the static or incremented offset of other bus buffers. Port A of two or more PCA9617As can be connected together, however, to allow a star topography with port A on the common bus, and port A can be connected directly to any other buffer with static or incremented offset outputs. Multiple PCA9617As can be connected in series, port A to port B, with no build-up in offset voltage with only time of flight delays to consider. The PCA9617ATPZ drivers are not enabled unless VCC(A) is above 0.8 V and VCC(B) is above 2.2 V. The EN pin is referenced to VCC(B) and can also be used to turn the drivers on and off under system control. Caution should be observed to only change the state of the enable pin when the bus is idle. The output pull-down on the port B internal buffer LOW is set for approximately 0.55 V, while the input threshold of the internal buffer is set about 90 mV lower (0.45 V). When the port B I/O is driven LOW internally, the LOW is not recognized as a LOW by the input. This prevents a latching condition from occurring. The output pull-down on port A drives a hard LOW and the input level is set 0.35VCC(A) to accommodate the need for a lower LOW level in systems where the low voltage side supply voltage is as low 0.8 V.

Table 2. Ordering options Orderable part number PCA9617ADPJ PCA9617ATPZ Package Packing method Minimum order quantity 2500 4000 Temperature range Type number

Features

Tape & Reel (TR) Package1 channels.

Mainly used in I2C.

ALSO OPERATES WITH 2.2 V TO 5.5 V.

Surface Mount Mounting Type

Applications

There are a lot of NXP USA Inc.

PCA9617ATPZ Signal Buffers, Repeaters, Splitters applications.

- PECL-to-LVDS Translation

- Cellular Phone Base Stations

- Add/Drop Muxes

- Digital Crossconnects

- Network Switches/Routers

- Backplane Interconnect

- Clock Distribution

- Protection Switching

- Loopback

- Clock Distribution

- 起步价为$40,南非、巴西、印度、巴基斯坦、以色列等国家的价格会有所变动,详情请咨询相关客服人员。

- 包裹重量≤0.5kg的基本运费根据时区和国家而定。

- 我们的产品目前使用DHL,顺丰和UPS运输。如果数量少,则选择联邦快递。

- 一旦发货,预期交货时间跟选择的运输方式有所变动。

准备产品

真空包装

防静电袋

单独包装

包装盒

条形码运输标签

NXP USA Inc.

NXP USA Inc.是NXP Semiconductors在美国的子公司,负责设计、研发、制造和销售半导体产品。公司在德克萨斯州奥斯汀和亚利桑那州钱德勒设有晶圆制造设施,专注于为汽车、工业和通信市场提供高性能解决方案。

热门零件号

实时新闻

博斯克数字

收入: 85M

2022年的收入为8500万美元,与2021年增长63%。

国家: 105

博斯克服务全球105个国家的客户。

配件发货: 25M+

我们在过去的五年中发货了2.5亿个配件,比前五年增长148%。

制造商: 950

2022年,博斯克从近950个制造商售卖了配件。

热门产品

A4989SLDTR-T

Allegro MicroSystems

IC MTR DRV BIPOLR 3-5.5V 38TSSOP

A3988SEVTR-T

Allegro MicroSystems

IC MTR DRVR BIPOLAR 3-5.5V 36QFN

A4982SLPTR-T

Allegro MicroSystems

IC MTR DRV BIPOLR 3-5.5V 24TSSOP

ACS713ELCTR-30A-T

Allegro MicroSystems

SENSOR CURRENT HALL 30A DC

ACS712ELCTR-05B-T

Allegro MicroSystems

SENSOR CURRENT HALL 5A AC/DC

A3938SLDTR-T

Allegro MicroSystems

IC MOTOR DRIVER 18V-50V 38TSSOP

A3906SESTR-T

Allegro MicroSystems

IC MTR DRVR BIPOLAR 2.5-9V 20QFN

ACS758LCB-100B-PFF-T

Allegro MicroSystems

SENSOR CURRENT HALL 100A 5-CB

A1326LLHLT-T

Allegro MicroSystems

SENSOR HALL EFFECT ANALOG SOT23W

ACS758LCB-100U-PFF-T

Allegro MicroSystems

SENSOR CURRENT HALL 100A 5-CB