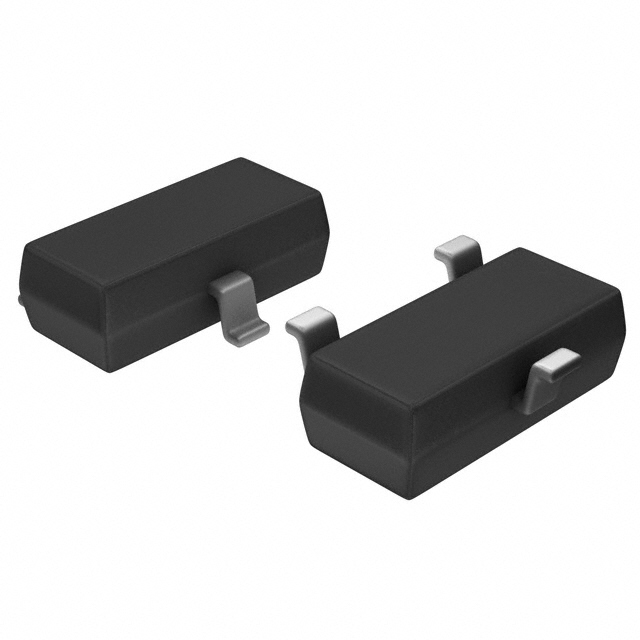

NS CDCF5801ADBQ

PLL 乘法器/除法器是HSTL、LVPECL、LVTTLHSTL、LVDS、LVPECL、LVTTL、SSTL

比较

¥30.69

价格更新:一个月前博斯克质量保证

Overview

The CDCF5801A provides clock multiplication from a reference clock (REFCLK) signal with the unique capability to delay or advance the CLKOUT/CLKOUTB with steps of only 1.3 mUI through a phase aligner. For every rising edge on the DLYCTRL pin the CLKOUT is delayed by a 1.3-mUI step size as long as the LEADLAG input detects a low signal at the time of the DLYCTRL rising edge. Similarly for every rising edge on the DLYCTRL pin the CLKOUT is advanced by a 1.3-mUI step size as long as the LEADLAG pin is high during the transition. This unique capability allows the device to phase align (zero delay) between CLKOUT/CLKOUTB and any one other CLK in the system by feeding the clocks that need to be aligned to the DLYCTRL and the LEADLAG pins. Also it provides the capability to program a fixed delay by providing the proper number of edges on the DLYCTRL pin, while strapping the LEADLAG pin to dc high or low. Further possible applications are:

The CDCF5801A provides clock multiplication and division from a reference clock (REFCLK) signal. The device is optimized to have extremely low jitter impact from input to output. The predivider pins MULT[0:1] and post-divider pins P[0:2] provide selection for frequency multiplication and division ratios, generating CLKOUT/CLOUTKB frequencies ranging from 25 MHz to 280 MHz with clock input references (REFCLK) ranging from 12.5 MHz to 240 MHz. Seefor detailed frequency support. The selection of pins MULT[0:1] and P[1:2] determines the multiplication value of 1, 2, 4, or 8. The CDCF5801A offers several power-down/ high-impedance modes, selectable by pins P0, STOPB and PWRDN. Another unique capability of the CDCF5801A is the high sensitivity and wide common-mode range of the clock-input pin REFCLK by varying the voltage on the VDDREF pin. The clock signal outputs CLKOUT and CLKOUTB can be used independently to generate single-ended clock signals. The CLKOUT/CLKOUTB outputs can also be combined to generate a differential output signal suitable for LVDS, LVPECL, or HSTL/SSTL signaling. The CDCF5801A is characterized for operation over free-air temperatures of -40°C to 85°C.

Features

Bulk PackageAvailable in the 24-SSOP (0.154, 3.90mm Width)

Supply voltage of 3.3V

Operating supply voltage of 3.3V

Surface Mount Mounting Type

Applications

There are a lot of Texas Instruments

CDCF5801ADBQ Clock Generators applications.

- Automatic test equipment

- Wide area power system

- Digital circuits

- Wireless base station for LTE, LTE-advanced

- Picocells, femtocells and small cells

- Sampling clocks for ADC and DAC

- 1 Gigabit Ethernet

- 10 Gigabit Ethernet

- FPGA and processor clocks

- Line cards used in telephone exchange

- 起步价为$40,南非、巴西、印度、巴基斯坦、以色列等国家的价格会有所变动,详情请咨询相关客服人员。

- 包裹重量≤0.5kg的基本运费根据时区和国家而定。

- 我们的产品目前使用DHL,顺丰和UPS运输。如果数量少,则选择联邦快递。

- 一旦发货,预期交货时间跟选择的运输方式有所变动。

准备产品

真空包装

防静电袋

单独包装

包装盒

条形码运输标签

National Semiconductor

National Semiconductor是一家著名的模拟半导体制造商,成立于1959年,总部位于美国加利福尼亚州圣克拉拉。2011年,National Semiconductor被德州仪器(Texas Instruments)收购,进一步增强了其在模拟半导体市场的领导地位。

实时新闻

博斯克数字

收入: 85M

2022年的收入为8500万美元,与2021年增长63%。

国家: 105

博斯克服务全球105个国家的客户。

配件发货: 25M+

我们在过去的五年中发货了2.5亿个配件,比前五年增长148%。

制造商: 950

2022年,博斯克从近950个制造商售卖了配件。

热门产品

ACS713ELCTR-30A-T

Allegro MicroSystems

SENSOR CURRENT HALL 30A DC

A4982SLPTR-T

Allegro MicroSystems

IC MTR DRV BIPOLR 3-5.5V 24TSSOP

A3938SLDTR-T

Allegro MicroSystems

IC MOTOR DRIVER 18V-50V 38TSSOP

ACS758LCB-100B-PFF-T

Allegro MicroSystems

SENSOR CURRENT HALL 100A 5-CB

ACS758LCB-100U-PFF-T

Allegro MicroSystems

SENSOR CURRENT HALL 100A 5-CB

A3906SESTR-T

Allegro MicroSystems

IC MTR DRVR BIPOLAR 2.5-9V 20QFN

A1326LLHLT-T

Allegro MicroSystems

SENSOR HALL EFFECT ANALOG SOT23W

A3988SEVTR-T

Allegro MicroSystems

IC MTR DRVR BIPOLAR 3-5.5V 36QFN

ACS712ELCTR-05B-T

Allegro MicroSystems

SENSOR CURRENT HALL 5A AC/DC

A4989SLDTR-T

Allegro MicroSystems

IC MTR DRV BIPOLR 3-5.5V 38TSSOP