AMD XC2C512-10FGG324C

系统内可编程9.2 ns32512270

比较

¥900.00

价格更新:一个月前博斯克质量保证

Overview

The CoolRunner-II 512-macrocell device is designed for both high performance and low power applications. This lends power savings to high-end communication equipment and high speed to battery operated devices. Due to the low power stand-by and dynamic operation, overall system reliability is improved This device consists of thirty two Function Blocks inter-connected by a low power Advanced Interconnect Matrix (AIM). The AIM feeds 40 true and complement inputs to each Function Block. The Function Blocks consist of a 40 by 56 P-term PLA and 16 macrocells which contain numerous configuration bits that allow for combinational or registered modes of operation. Additionally, these registers can be globally reset or preset and configured as a D or T flip-flop or as a D latch. There are also multiple clock signals, both global and local product term types, configured on a per macrocell basis. Output pin configurations include slew rate limit, bus hold, pull-up, open drain and programmable grounds.

A Schmitt-trigger input is available on a per input pin basis. In addition to storing macrocell output states, the macrocell registers may be configured as "direct input" registers to store signals directly from input pins. Clocking is available on a global or Function Block basis. Three global clocks are available for all Function Blocks as a synchronous clock source. Macrocell registers can be individually configured to power up to the zero or one state. A global set/reset control line is also available to asynchronously set or reset selected registers during operation. Additional local clock, synchronous clock-enable, asynchronous set/reset and output enable signals can be formed using product terms on a per-macrocell or per-Function Block basis. A DualEDGE flip-flop feature is also available on a per macrocell basis. This feature allows high performance synchronous operation based on lower frequency clocking to help reduce the total power consumption of the device. Circuitry has also been included to divide one externally supplied global clock (GCK2) by eight different selections. This yields divide by even and odd clock frequencies.

Features

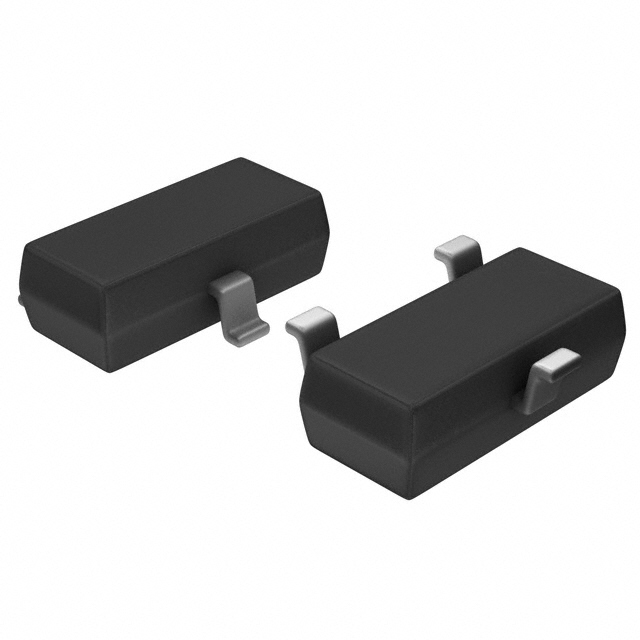

CoolRunner II Series324-BBGA package

270 I/Os

The operating temperature of 0°C~70°C TA

324 pin count

324 pins

Surface Mount Mounting Type

Applications

There are a lot of Xilinx Inc.

XC2C512-10FGG324C CPLDs applications.

- Digital systems

- Portable digital devices

- Handheld digital devices

- Battery operated portable devices

- Complex programmable logic devices

- Digital designs

- Field programmable gate

- Address decoding

- D/T registers and latches

- Synchronous or asynchronous mode

- 起步价为$40,南非、巴西、印度、巴基斯坦、以色列等国家的价格会有所变动,详情请咨询相关客服人员。

- 包裹重量≤0.5kg的基本运费根据时区和国家而定。

- 我们的产品目前使用DHL,顺丰和UPS运输。如果数量少,则选择联邦快递。

- 一旦发货,预期交货时间跟选择的运输方式有所变动。

准备产品

真空包装

防静电袋

单独包装

包装盒

条形码运输标签

XC2C384-10TQ144I

Xilinx

IC CPLD 384MC 9.2NS 100TQFP

XC2C384-7TQ144C

Xilinx

IC CPLD 384MC 7.1NS 100TQFP

XC2C384-7FTG256C

Xilinx

IC CPLD 384MC 7.1NS 256FTBGA

XC2C384-7FT256C

Xilinx

IC CPLD 384MC 7.1NS 256FTBGA

XC2C512-10FG324I

Xilinx

IC CPLD 512MC 9.2NS 324FBGA

XC2C384-7PQ208C

Xilinx

IC CPLD 384MC 7.1NS 208QFP

AMD

Advanced Micro Devices (AMD)是一家全球领先的半导体公司,专注于开发高性能计算和图形处理解决方案。公司成立于1969年,总部位于美国加利福尼亚州圣克拉拉。AMD的产品广泛应用于个人计算机、数据中心、游戏和嵌入式系统等领域。

实时新闻

博斯克数字

收入: 85M

2022年的收入为8500万美元,与2021年增长63%。

国家: 105

博斯克服务全球105个国家的客户。

配件发货: 25M+

我们在过去的五年中发货了2.5亿个配件,比前五年增长148%。

制造商: 950

2022年,博斯克从近950个制造商售卖了配件。

热门产品

ACS713ELCTR-30A-T

Allegro MicroSystems

SENSOR CURRENT HALL 30A DC

A4989SLDTR-T

Allegro MicroSystems

IC MTR DRV BIPOLR 3-5.5V 38TSSOP

ACS758LCB-100B-PFF-T

Allegro MicroSystems

SENSOR CURRENT HALL 100A 5-CB

ACS758LCB-100U-PFF-T

Allegro MicroSystems

SENSOR CURRENT HALL 100A 5-CB

A3938SLDTR-T

Allegro MicroSystems

IC MOTOR DRIVER 18V-50V 38TSSOP

A4982SLPTR-T

Allegro MicroSystems

IC MTR DRV BIPOLR 3-5.5V 24TSSOP

A1326LLHLT-T

Allegro MicroSystems

SENSOR HALL EFFECT ANALOG SOT23W

A3906SESTR-T

Allegro MicroSystems

IC MTR DRVR BIPOLAR 2.5-9V 20QFN

ACS712ELCTR-05B-T

Allegro MicroSystems

SENSOR CURRENT HALL 5A AC/DC

A3988SEVTR-T

Allegro MicroSystems

IC MTR DRVR BIPOLAR 3-5.5V 36QFN